# 12bit 2 channels SAR AD converter IC

# MM3804A12RLE Datasheet

# **FUNCTION**

12-Bit Two Channels Successive Approximation Type Analog to Digital Converter IC.

# **FEATURES**

- · High sampling rate: 750Ksps

- · Pseudo differential analog inputs

- · Two-channel simultaneous sampling

# **INDEX**

| FUNCTION                                     |    |

|----------------------------------------------|----|

| FEATURES                                     |    |

| BLOCK DIAGRAM                                | 3  |

| PIN CONFIGURATION                            | 2  |

| TERMINAL EXPLANATIONS                        |    |

| ABSOLUTE MAXIMUM RATINGS                     |    |

| RECOMMENDED OPERATING CONDITIONS             | -  |

| ELECTRICAL CHARACTERISTICS                   | 8  |

| TIMING CHARACTERISTICS                       | 1  |

| DETAILED DESCRIPTION                         |    |

| OVERVIEW                                     |    |

| ANALOG TO DIGITAL CONVERSION                 |    |

| Short cycle read                             |    |

| Conversion abort, Reconversion, Power-on     |    |

| ANALOG INPUT                                 |    |

| DATA FORMAT                                  |    |

| TYPICAL APPLICATION CIRCUIT                  | 16 |

| TYPICAL PERFOR MANCE CHARACTERISTICS         | 17 |

| DIMENSIONS                                   |    |

| MARKING CONTENTS                             | 20 |

| How to identify 3 characteristic lot numbers | 2  |

| NOTES                                        | 22 |

| ATTENTION                                    | 23 |

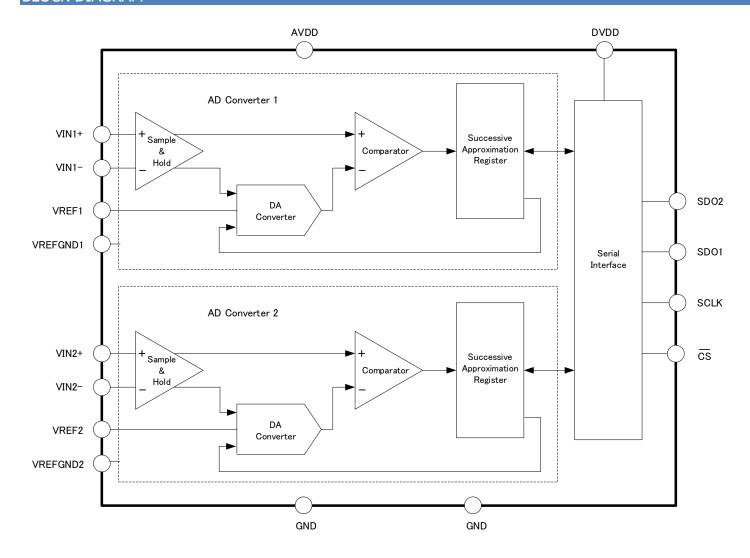

# **BLOCK DIAGRAM**

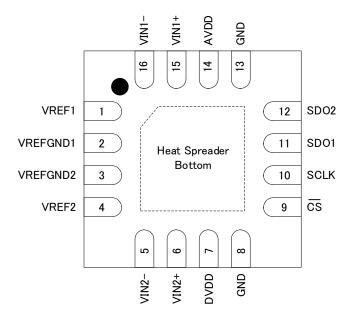

# PIN CONFIGURATION

# TERMINAL EXPLANATIONS

| PIN No. | SYMBOL   | TYPE   | INTERNAL EQUIVALENT CIRCUIT | FUNCTION                         |

|---------|----------|--------|-----------------------------|----------------------------------|

| 1       | VREF1    | Input  | AVDD O                      | Reference voltage input for ADC1 |

| 2       | VREFGND1 | Supply | VREF1 C                     | Reference voltage GND for ADC1   |

| 3       | VREFGND2 | Supply | VREF2 VREFGND1 VREFGND2     | Reference voltage GND for ADC2   |

| 4       | VREF2    | Input  | GND ///                     | Reference voltage input for ADC2 |

| 5       | VIN2-    | Input  | VIN2-<br>VIN2+              | Minus analog input for ADC2      |

| 6       | VIN2+    | Input  | GND ///                     | Plus analog input for ADC2       |

| 7       | DVDD     | Supply | DVDD GND GND                | Power supply for digital I/O     |

| 8       | GND      | Supply | -                           | Ground                           |

| 9       | CS       | Input  |                             | Chip select input                |

| 10      | SCLK     | Input  | CS SCLK GND ///             | Serial communication clock input |

| PIN No. | SYMBOL | TYPE   | INTERNAL EQUIVALENT CIRCUIT | FUNCTION                                  |

|---------|--------|--------|-----------------------------|-------------------------------------------|

| 11      | SDO1   | Output | DVDD O                      | Serial communication data output for ADC1 |

| 12      | SDO2   | Output | SDO1<br>SDO2<br>GND /// GND | Serial communication data output for ADC2 |

| 13      | GND    | Supply | -                           | Ground                                    |

| 14      | AVDD   | Supply | AVDD GND GND                | Power supply for ADC                      |

| 15      | VIN1+  | Input  | VIN1-<br>VIN1+              | Plus analog input for ADC1                |

| 16      | VIN1-  | Input  | GND ///                     | Minus analog input for ADC1               |

# ABSOLUTE MAXIMUM RATINGS

| ITEM                         | SYMBOL               | MIN.    | MAX.     | UNIT  |

|------------------------------|----------------------|---------|----------|-------|

| Supply voltage               | AVDD<br>DVDD         | -0.3    | 7.0      | V     |

| Analog input voltage         | (note <sup>1</sup> ) | GND-0.3 | AVDD+0.3 | V     |

| Digital input voltage        | (note <sup>2</sup> ) | GND-0.3 | DVDD+0.3 | V     |

| Ground voltage difference    | GNDd                 | -       | 0.3      | V     |

| Storage temperature          | Tstg                 | -65     | 150      | deg.C |

| Power dissipation (On board) | Pd                   | -       | 2.7      | W     |

note<sup>1</sup>: VIN1+, VIN1-, VREF1, VIN2+, VIN2-, VREF2

note<sup>2</sup>:  $\overline{CS}$ , SCLK,SDO1,SDO2

# RECOMMENDED OPERATING CONDITIONS

| ITEM                          | SYMBOL | MIN. | TYP. | MAX. | UNIT  |

|-------------------------------|--------|------|------|------|-------|

| Operating ambient temperature | Тор    | -40  | -    | 125  | deg.C |

| AVDD operating voltage        | AVDDop | 4.5  | 5    | 5.5  | V     |

| DVDD operating voltage        | DVDDop | 1.65 | 3.3  | 5.5  | V     |

# ELECTRICAL CHARACTERISTICS

(Unless otherwise specified, Ta=25deg.C, AVDD=5V, DVDD=3.3V, VREF1=VREF2=2.5V, Sampling rate (fsample) =750Ksps)

| (Unless otherwise specified, Ta=25deg.C, AVDD=5V, DVDD=3.3V, VREF1=VREF2=2.5V, Sampling rate (fsample) =750Ks |                   |                              |          |      | e) =/50KSpS) |      |

|---------------------------------------------------------------------------------------------------------------|-------------------|------------------------------|----------|------|--------------|------|

| PARAMETER                                                                                                     | SYMBOL            | CONDITIONS                   | MIN.     | TYP. | MAX.         | UNIT |

| Power supply                                                                                                  |                   |                              |          |      |              |      |

| Analog supply current (operational)                                                                           | Iavop             | AVDD=5V,<br>fsample=750ksps  | -        | 6.0  | 7.0          | mA   |

| Analog supply current (static)                                                                                | Iavst             | AVDD=5V,<br>CS=H             | -        | 4.0  | 6.0          | mA   |

| Digital supply current                                                                                        | $\mathrm{I}_{dv}$ | DVDD=3.3V<br>fsample=750ksps | -        | 0.20 | -            | mA   |

| Analog input                                                                                                  |                   |                              |          |      |              |      |

| Full-scale input range                                                                                        | FSR               | (note <sup>3</sup> )         | -Vref    | -    | Vref         | V    |

| Absolute input voltage (+)                                                                                    | Vin+              | (note <sup>3</sup> )         | 0.0      | -    | 2×Vref       | V    |

| Absolute input voltage (-)                                                                                    | Vin-              |                              | Vref-0.1 | Vref | Vref+0.1     | V    |

| Innut conscitoned (note4)                                                                                     | Cina              | Sample mode                  | -        | 15   | -            | pF   |

| Input capacitance (note <sup>4</sup> )                                                                        | Cina              | Hold mode                    | -        | 4    | -            | pF   |

| Input leakage current                                                                                         | Iina              |                              | -        | 1.5  | -            | nA   |

| Reference voltage input                                                                                       |                   |                              |          |      |              |      |

| Reference input voltage                                                                                       | Vref              |                              | 2.25     | 2.5  | AVDD/2       | V    |

| Current drain                                                                                                 | Iref              |                              | -        | 300  | 600          | μΑ   |

|                                                                                                               | Irefl             | CS=AVDD                      | -        | 0    | 1            | μΑ   |

note<sup>3</sup>: Each of the following conditions is required to use this IC with the maximum dynamic range.

$FSR\_ADC1 = 2 \times VREF1$ ,  $FSR\_ADC2 = 2 \times VREF2$

VIN1+ = 0 to  $2 \times VREF1$ , VIN2+ = 0 to  $2 \times VREF2$

ViIN1- = VREF1, ViIN2- = VREF2

AVDD ≥ 2×VREF1, AVDD ≥ 2×VREF2

note<sup>4</sup>: Specified by design

(Unless otherwise specified. Ta=25deg.C, AVDD=5V, DVDD=3.3V, VREF1=VREF2=2.5V, Sampling rate (fsample) =750Ksps)

| (Unless otherwise specified.                    | Ta=25deg.C,      | AVDD=5V, DVDD=3.3V, VREF                           | 1=VREF2=2. | 5V, Sampling | rate (fsample | e) =/50Ksps)                |

|-------------------------------------------------|------------------|----------------------------------------------------|------------|--------------|---------------|-----------------------------|

| PARAMETER                                       | SYMBOL           | CONDITIONS                                         | MIN.       | TYP.         | MAX.          | UNIT                        |

| Resolution                                      |                  |                                                    |            |              |               |                             |

| Resolution                                      | Reso             |                                                    | -          | -            | 12            | Bits                        |

| Sampling dynamics                               |                  |                                                    |            |              |               |                             |

| Data rate                                       | fsample          |                                                    | -          | -            | 750           | Ksps                        |

| Aperture delay<br>(note <sup>5</sup> )          | tap              |                                                    | -          | 4            | -             | ns                          |

| Clock frequency                                 | f <sub>clk</sub> |                                                    | -          | -            | 24            | MHz                         |

| DC accuracy                                     |                  |                                                    |            |              |               |                             |

| Integral nonlinearity                           | INL              |                                                    | -2         | -            | 2             | LSB<br>(note <sup>6</sup> ) |

| Differential nonlinearity                       | DNL              |                                                    | -1         | -            | 2             | LSB                         |

| Input offset error                              | Vof              |                                                    | -2         | -            | 2             | LSB                         |

| Input offset thermal drift (note <sup>5</sup> ) | dVof/dt          |                                                    | -          | 0.01         | -             | LSB<br>/deg.C               |

| Gain error                                      | Gerr             | Refers to the voltage of VREF1 and VREF2.          | -4         | -            | 4             | LSB                         |

| Gain error thermal drift (note <sup>5</sup> )   | Gerr/dt          | Refers to the voltage of VREF1 and VREF2.          | -          | 0.004        | -             | LSB<br>/deg.C               |

| Common mode rejection ratio                     | CMRR             | Signals of DC to 20kHz are input to ADC1 and ADC2. | -          | 70           | -             | dB                          |

note<sup>5</sup>: Specified by design

note<sup>6</sup>: When VREF is 2.5V, 1 LSB is 1.22mV.

(Unless otherwise specified. Ta=25deg.C, AVDD=5V, DVDD=3.3V, VREF1=VREF2=2.5V, Sampling rate (fsample) =750Ksps)

| PARAMETER                            | SYMBOL           | CONDITIONS                                        | MIN.         | TYP. | MAX.          | UNIT |

|--------------------------------------|------------------|---------------------------------------------------|--------------|------|---------------|------|

| AC accuracy                          |                  |                                                   |              |      |               |      |

|                                      |                  | -0.5dB [full scale]<br>at 20kHz input             | -            | -76  | -             | dB   |

| Total harmonic distortion            | THD              | -0.5dB [full scale]<br>at 100kHz input            | -            | -75  | -             | dB   |

|                                      |                  | -0.5dB [full scale]<br>at 250kHz input            | -            | -72  | -             | dB   |

|                                      |                  | -0.5dB [full scale]<br>at 20kHz input             | -            | 70   | -             | dB   |

| Signal to (noise + distortion) ratio | SINAD            | -0.5dB [full scale]<br>at 100kHz input            | -            | 69   | -             | dB   |

|                                      |                  | -0.5dB [full scale]<br>at 250kHz input            | -            | 67   | -             | dB   |

|                                      |                  | -0.5dB [full scale]<br>at 20kHz input             | -            | 71   | -             | dB   |

| Signal to noise ratio                | SNR              | -0.5dB [full scale]<br>at 100kHz input            | -            | 70   | -             | dB   |

|                                      |                  | -0.5dB [full scale]<br>at 250kHz input            | -            | 68   | -             | dB   |

|                                      | SFDR             | -0.5dB [full scale]<br>at 20kHz input             | -            | 78   | -             | dB   |

| Spurious free dynamic range          |                  | -0.5dB [full scale]<br>at 100kHz input            | -            | 77   | -             | dB   |

| runge                                |                  | -0.5dB [full scale]<br>at 250kHz input            | -            | 74   | -             | dB   |

| Isolation between ADC1 and ADC2      | Iso12            | f <sub>IN</sub> =15kHz, f <sub>NOISE</sub> =25kHz | -            | -85  | -             | dB   |

|                                      | DIM              | -3dB                                              | -            | 25   | -             | MHz  |

| Full power bandwidth                 | BW <sub>FP</sub> | -0.1dB                                            | -            | 5    | -             | MHz  |

| Digital input (note <sup>7</sup> )   |                  |                                                   |              |      |               |      |

| High level input voltage             | Vih              |                                                   | 0.7×<br>DVDD | -    | DVDD<br>+0.3  | V    |

| Low level input voltage              | Vil1             | DVDD≧2V                                           | -0.30        | -    | 0.3×<br>DVDD  | V    |

| Low level input voltage              | Vil2             | DVDD<2V                                           | -0.30        | -    | 0.15×<br>DVDD | V    |

| Digital output (note <sup>7</sup> )  | •                |                                                   | •            | •    | •             |      |

| High level output voltage            | Voh              | Ioh=500μA<br>source                               | 0.8×<br>DVDD | -    | DVDD          | V    |

| Low level output voltage             | Vol              | Iol=500μA<br>sink                                 | 0            | -    | 0.2×<br>DVDD  | V    |

|                                      |                  | Sillic                                            |              | L    | D 1 D D       | L    |

note<sup>7</sup>: Specified by design

# TIMING CHARACTERISTICS

(Unless otherwise specified. Ta=25deg.C, AVDD=5V, DVDD=3.3V, VREF1=VREF2=2.5V, Sampling rate (fsample) =750Ksps)

| PARAMETER                      | SYMBOL              | CONDITIONS             | MIN. | TYP. | MAX. | UNIT            |

|--------------------------------|---------------------|------------------------|------|------|------|-----------------|

| Data rate                      | f <sub>SAMPLE</sub> |                        | -    | -    | 750  | Ksps            |

| Clock frequency                | f <sub>CLK</sub>    |                        | -    | -    | 24   | MHz             |

| Clock duty                     | Duty                |                        | 40   | -    | 60   | %               |

| Conversion time                | tconv               |                        | -    | -    | 15   | clock<br>cycles |

| Acquisition time               | t <sub>ACQ</sub>    | f <sub>ck</sub> =24MHz | 70   | -    | -    | ns              |

| CS high time                   | tcs                 |                        | 20   | -    | -    | ns              |

| CS high time after frame abort | t <sub>CSa</sub>    |                        | 70   | -    | -    | ns              |

| SCLK setup time                | tcsck               |                        | 15   | -    | -    | ns              |

| SDO Delay time                 | t <sub>CKDO</sub>   |                        | 3    | -    | 20   | ns              |

| SDO tristate delay time 1      | tcsdoi              |                        | -    | -    | 12   | ns              |

| SDO tristate delay time 2      | tcspot              |                        | -    | -    | 10   | ns              |

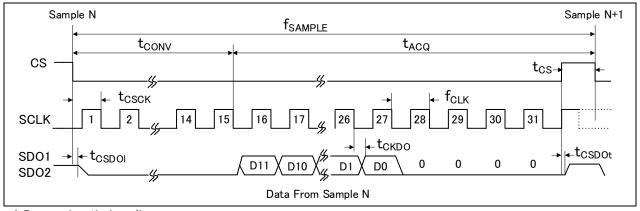

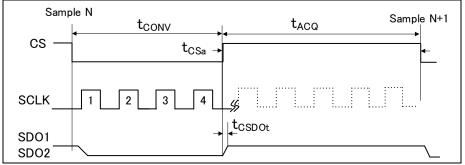

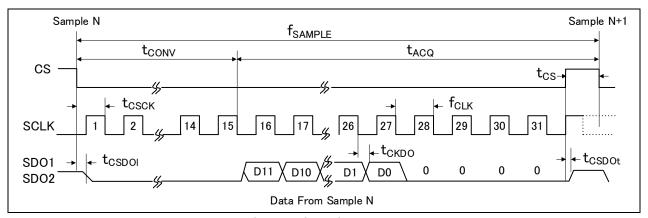

· Normal Conversion timing diagram

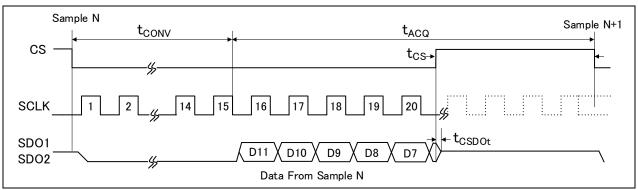

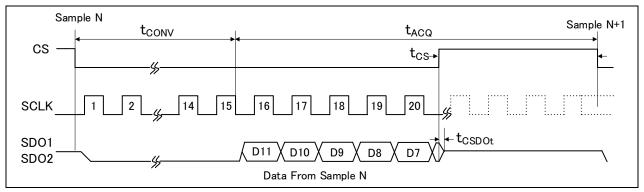

· Short cycle read timing diagram

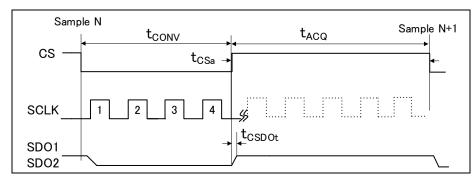

· Abort timing diagram

Fig. 1 Analog to digital conversion timing diagram

## **DETAILED DESCRIPTION**

#### **OVERVIEW**

MM3804A12 is a successive approximation type of AD converter IC, which can simultaneously convert two analog signals to 12-bit data at 750 Ksps at the maximum. This IC supports pseudo-differential input of analog signals. SPI is used for communication with an external digital host.

## ANALOG TO DIGITAL CONVERSION

Fig. 2 shows a timing diagram. MM3804A12 requires a minimum of 26-SCLK falling edge between CS falling edge and CS rising edge to perform 12-bit analog to digital conversion. The conversion is started from the CS falling edge, and the sampled analog values are converted to digital values during 15 SCLKs. The values output from SDO1 and SDO2 are "0" during this conversion period.

The sample and hold circuit returns to the sampling mode at the 15th SCLK falling edge. Moreover, the MSBs of ADC1 and ADC2 are output to SDO1 and SDO2 respectively at the 15th SCLK falling edge. From the next falling edge, the conversion results are successively output, and LSBs are output at the 26th-SCLK falling edge. If  $\overline{\text{CS}}$  low continues, SDO1 and SDO2 output "0" from the 27th-SCLK falling edge to the  $\overline{\text{CS}}$  rising edge. The conversion frame ends at the  $\overline{\text{CS}}$  rising edge, and SDO1 and SDO2 become Hi-Z.

Fig. 2 Analog to digital conversion timing

## Short cycle read

Fig. 3 shows a short cycle read timing diagram. Sampled input analog values are converted to digital values during 15 CLKs. From the 15th SCLK falling edge, the conversion results are successively output to SDO1 and SDO2 in MSB first order. If the CS is made high before the 26th SCLK falls, the successive outputs from SDO1 and SDO2 will be Hi-Z.

The output data from SDO1 and SDO2 before the CS is made high is valid. In some cases, CS high period must be kept after conversion abort to set aside enough time to collect analog signals until the next conversion frame.

Fig. 3 Short cycle read

## Conversion abort, Reconversion, Power-on

When CS is changed to high before the 15th SCLK falls, the conversion is aborted and sampling of the next analog input signal is started (Fig. 4). CS high period must be kept after conversion abort to set aside enough time to collect analog signals until the next conversion frame. Additionally, abnormal data may be output due to lack of the time to collect analog signals for the first conversion because this IC is reset at the first CS rising edge when the power is turned on. In this case, the initial data should be discarded.

Fig. 4 Conversion abort

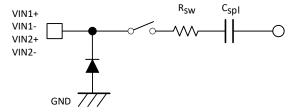

## **ANALOG INPUT**

MM3804A12 supports pseudo-differential input of analog signals. There are two channels of analog input and simultaneous sampling is possible. Fig. 5 shows an equivalent circuit of analog input. A diode is connected to pins for ESD protection.

Fig. 5 Equivalent analog input circuit

## **DATA FORMAT**

The data output from SDO1 and SDO2 is in two's complement binary format. Table 1 shows analog input voltage and ideal output codes.

Table 1 Differential analog input voltage and ideal output codes

|                     |       | Input voltage  | Pseudo differential input    | Output code    |     |

|---------------------|-------|----------------|------------------------------|----------------|-----|

| State               | VIN*- | VIN*+          | voltage<br>(VIN*+) - (VIN*-) | BIN            | HEX |

| +Full scale         |       | 2×VREF* - 1LSB | VREF* - 1LSB                 | 0111 1111 1111 | 7FF |

| Middle scale        |       | VREF*          | 0                            | 0000 0000 0000 | 000 |

| Middle scale - 1LSB | VREF* | VREF* - 1LSB   | -1LSB                        | 1111 1111 1111 | FFF |

| 1LSB                |       | 1LSB           | -VREF* + 1LSB                | 1000 0000 0001 | 801 |

| -Full scale         |       | 0              | -VREF*                       | 1000 0000 0000 | 800 |

VIN\*+, VIN\*-, VREF\*:VIN1+, VIN1-, VREF1 or VIN2+, VIN2-, VREF2 1LSB=FSR/2<sup>12</sup>=FSR/4096 VREF\* equal to 2.5V, 1LSB is 1.22mV

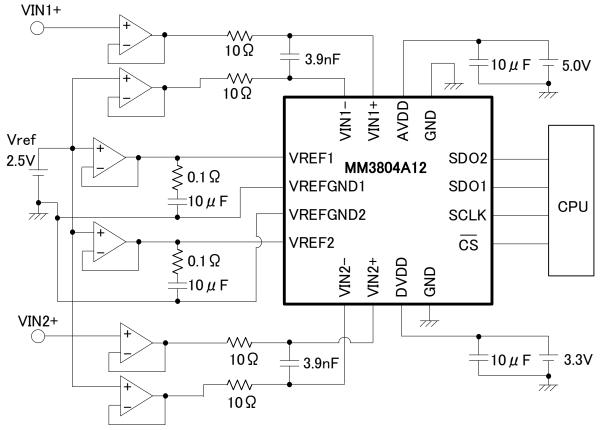

## TYPICAL APPLICATION CIRCUIT

Fig. 6 Typical application circuit for 10KHz input signal at 750Ksps

#### **APPLICATION HINTS**

- · A ceramic capacitor of 1µF to 10µF must be connected near AVDD and DVDD, respectively. This improves voltage ripple and resistance to external noises, and stabilizes the system.

- · VREF1 and VREFGND1 pins must be separated from VREF2 and VREFGND2 pins. A resistor of  $0.1\Omega$  must be connected to the ceramic capacitor of  $1\mu F$  to  $10\mu F$  in series near and between VREF1 and VREFGND1 and between VREF2 and VREFGND2 for stabilization.

- And It is recommended the capacitance value be verified with the actual device.

- · High frequency components must be removed from signals input to the analog input pin using an RC low-pass filter. The capacitor not only removes high frequency components from input signals but also reduces the sampling charge injection of the sampling capacitor in ADC. It is recommended that the filter constant be verified with the actual device.

- · AVDD, DVDD, GND, VREFGND1, and VREFGND2 wires must be sufficiently strengthened because they may cause noises and unstable operations when their impedance is high.

- · AVDD and GND pins and DVDD and GND pins are positioned side by side, respectively. If short circuit occurs during board mounting, peripheral devices may be destroyed.

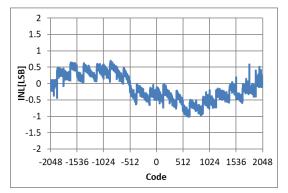

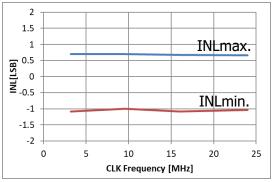

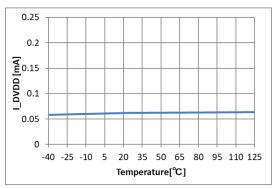

## TYPICAL PERFOR MANCE CHARACTERISTICS

Fig. 7 INL

Fig. 9 INL vs SCLK Frequency

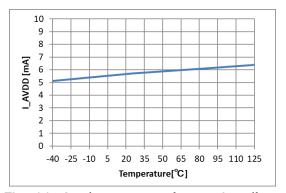

Fig. 11 Analog current (operational) vs Temperature

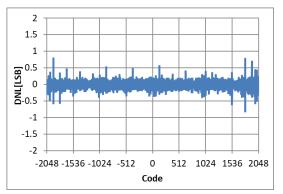

Fig. 8 DNL

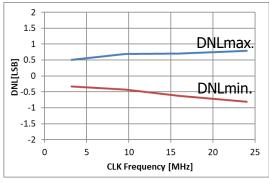

Fig. 10 DNL vs SCLK Frequency

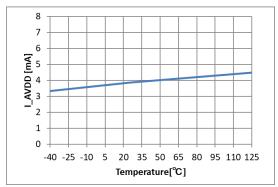

Fig. 12 Analog current (static) vs Temperature

Fig. 13 Digital current vs Temperature

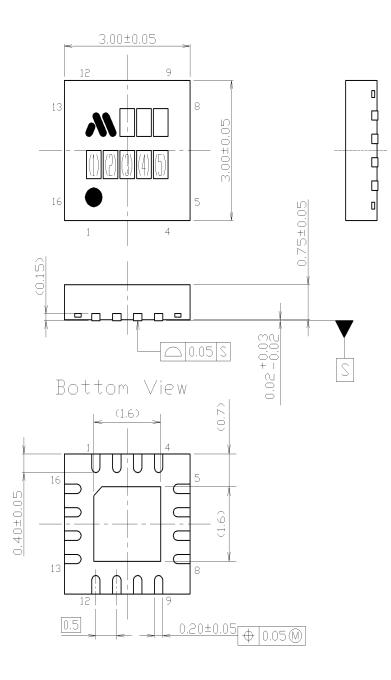

# **DIMENSIONS**

PACKAGE: SQFN-16A

UNIT mm

No.R16-SQFN16A-0001

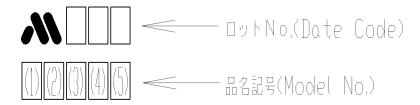

# MARKING CONTENTS

| Model name                |     | M   | odel N | 0.  |     |

|---------------------------|-----|-----|--------|-----|-----|

| M M 3 8 0 4 A 1 2 R x x 8 | (1) | (2) | (3)    | (4) | (5) |

|                           | 8   | 0   | 4      | Α   | 2   |

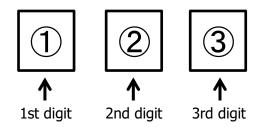

# How to identify 3 characteristic lot numbers.

- 1. The 1st digit (1) shows the last digit of a production year (western calendar).

- 2. The 2nd (②) and 3rd (③) digit show a production week of mass production.

## [How to indicate a production year]

| The 1st digit (①)                            |      |  |  |  |  |  |

|----------------------------------------------|------|--|--|--|--|--|

| the last<br>digit of a<br>production<br>year | mark |  |  |  |  |  |

| xxx1                                         | 1    |  |  |  |  |  |

| xxx2                                         | 2    |  |  |  |  |  |

| xxx3                                         | 3    |  |  |  |  |  |

| xxx4                                         | 4    |  |  |  |  |  |

| xxx5                                         | 5    |  |  |  |  |  |

| xxx6                                         | 6    |  |  |  |  |  |

| xxx7                                         | 7    |  |  |  |  |  |

| xxx8                                         | 8    |  |  |  |  |  |

| xxx9                                         | 9    |  |  |  |  |  |

| xxx0                                         | 0    |  |  |  |  |  |

| The 2nd and 3rd digit (2(3)) |      |                 |      |

|------------------------------|------|-----------------|------|

| production week              | mark | production week | mark |

| 1                            | 01   | 27              | 27   |

| 2                            | 02   | 28              | 28   |

| 3                            | 03   | 29              | 29   |

| 4                            | 04   | 30              | 30   |

| 5                            | 05   | 31              | 31   |

| 6                            | 06   | 32              | 32   |

| 7                            | 07   | 33              | 33   |

| 8                            | 08   | 34              | 34   |

| 9                            | 09   | 35              | 35   |

| 10                           | 10   | 36              | 36   |

| 11                           | 11   | 37              | 37   |

| 12                           | 12   | 38              | 38   |

| 13                           | 13   | 39              | 39   |

| 14                           | 14   | 40              | 40   |

| 15                           | 15   | 41              | 41   |

| 16                           | 16   | 42              | 42   |

| 17                           | 17   | 43              | 43   |

| 18                           | 18   | 44              | 44   |

| 19                           | 19   | 45              | 45   |

| 20                           | 20   | 46              | 46   |

| 21                           | 21   | 47              | 47   |

| 22                           | 22   | 48              | 48   |

| 23                           | 23   | 49              | 49   |

| 24                           | 24   | 50              | 50   |

| 25                           | 25   | 51              | 51   |

| 26                           | 26   | 52              | 52   |

|                              |      | 53              | 53   |

The 2nd and 3rd digit (23)

## NOTES

## **Safety Precautions**

- Though Mitsumi Electric Co., Ltd. (hereinafter referred to as "Mitsumi") works continually to improve our product's quality and reliability, semiconductor products may generally malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of this product could cause loss of human life, bodily injury, or damage to property, including data loss or corruption. Before customers use this product, create designs including this product, or incorporate this product into their own applications, customers must also refer to and comply with (a) the latest versions or all of our relevant information, including without limitation, product specifications, data sheets and application notes for this product and (b) the user's manual, handling instructions or all relevant information for any products which is to be used, or combined with this products. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. Mitsumi assumes no liability for customers' product design or applications.

- This product is intended for applying to computers, OA units, communication units, instrumentation units, machine tools, industrial robots, AV units, household electrical appliances, and other general electronic units.

- This product is not designed as a component of equipment or devices that require a high degree of reliability, may affect the life or body, or could damage the property (space systems, submarine repeaters, nuclear power controllers, infrastructure controllers, medical equipment, military devices, units related to the control and safety of transport equipment (automobiles, trains, aircraft, etc.), traffic signaling equipment, disaster / crime prevention units, or the like). In the case where this product is used in these applications, Mitsumi does not bear any responsibility. If the product is used as a component of the above equipment or devices, Mitsumi shall not be liable for any damage caused thereby. It is the customer's responsibility to carry out the necessary safety design for the customer's hardware, software and systems.

- · Before using this product, even when it is not used for the applications written previous paragraph, notify and present us beforehand if special care and attention are needed for its application, intended purpose, environment of usage, risk, and the design or inspection specification corresponding to them.

- If any damage to our customer is objectively identified to be caused by the defect of this product, Mitsumi is responsible for it. In this case, Mitsumi is liable for the cost limited to the delivery price of this product.

## Application considerations during actual circuit design

- The outline of parameters described herein has been chosen as an explanation of the standard parameters and performance of the product. When you actually plan to use the product, please ensure that the outside conditions are reflected in the actual circuit and assembling designs.

- · Before using this product, please evaluate and confirm the actual application with this product mounted and embedded.

- To investigate the influence by applied transient load or external noise, It is necessary to evaluate and confirm them with mounting this product to the actual application.

- Any usage above the maximum rating may destroy this product or shorten the lifetime. Be sure to use this product under the maximum rating.

- · If you continue to use this product highly-loaded (applying high temperature, large current or high voltage; or variation of temperature) even under the absolute maximum rating and even in the operating range, the reliability of this product may decrease significantly. Please design appropriate reliability in consideration of power dissipation and voltage corresponding to the temperature and designed lifetime after confirming our individual reliability documents (such as reliability test report or estimated failure rate). It is recommended that, before using this product, you appropriately derate the maximum power dissipation (typically, 80% or less of the maximum value) considering parameters including ambient temperature, input voltage, and output current.

#### **Precautions for Foreign Exchange and Foreign Trade Control Act**

· If you export or take products and technologies in this document which are subject to security trade control based on the Foreign Exchange and Foreign Trade Act to overseas from Japan, permission of the Japanese government is required.

## **Prohibitions for Industrial Property Rights**

- Since this document contains the contents related to our copyright and know-how, you are requested not to use this document for any purpose other than the application of this product.

- If a use of this product causes a dispute related to the industrial property rights of a third party, Mitsumi has no liability for any disputes except those which arise directly from the manufacturing and manufacturing method of our products.

## **Precautions for Product Liability Act**

· Mitsumi does not bear any responsibility for any consequence resulting from any wrong or improper use of this product and other factors.

#### **Others**

- · Any part of the contents contained herein must not be reprinted or reproduced without our prior permission.

- In case of any question arises out of the description in this specification, it shall be settled by the consultation between both parties promptly.

## **ATTENTION**

· This product is designed and manufactured with the intention of normal use in general electronics. No special circumstance as described below is considered for the use of it when it is designed. With this reason, any use and storage under the circumstances below may affect the performance of this product. Prior confirmation of performance and reliability is requested to customers.

Environment with strong static electricity or electromagnetic wave

Environment with high temperature or high humidity where dew condensation may occur

• This product is not designed to withstand radioactivity, and must avoid using in a radioactive environment.

# MITSUMI ELECTRIC CO., LTD.

Strategy Engineering Department Semiconductor Business Division

Tel: +81-46-230-3470 / <a href="https://product.minebeamitsumi.com/en/contact/">https://product.minebeamitsumi.com/en/contact/</a>

#### Notes

Any products mentioned this datasheet are subject to any modification in their appearance and others for improvements without prior notification. The details listed here are not a guarantee of the individual products at the time of ordering. When using the products, you will be asked to check their specifications

©2024 Mitsumi Electric Co., Ltd. All rights reserved. The contents of this document are subject to change without notice. The details listed here are not a guarantee.

# Disclaimers (Handling Precautions)

- 1. All the information described herein (product data, specifications, figures, tables, programs, algorithms and application circuit examples, etc.) is current as of publishing date of this document and is subject to change without notice.

- 2. The circuit examples and the usages described herein are for reference only, and do not guarantee the success of any specific mass-production design.

- MITSUMI ELECTRIC CO., LTD. is not liable for any losses, damages, claims or demands caused by the reasons other than the products described herein (hereinafter "the products") or infringement of third-party intellectual property right and any other right due to the use of the information described herein.

- 3. MITSUMI ELECTRIC CO., LTD. is not liable for any losses, damages, claims or demands caused by the incorrect information described herein.

- 4. Be careful to use the products within their ranges described herein. Pay special attention for use to the absolute maximum ratings, operation voltage range and electrical characteristics, etc.

- MITSUMI ELECTRIC CO., LTD. is not liable for any losses, damages, claims or demands caused by failures and / or accidents, etc. due to the use of the products outside their specified ranges.

- 5. Before using the products, confirm their applications, and the laws and regulations of the region or country where they are used and verify suitability, safety and other factors for the intended use.

- 6. When exporting the products, comply with the Foreign Exchange and Foreign Trade Act and all other export-related laws, and follow the required procedures.

- 7. The products are strictly prohibited from using, providing or exporting for the purposes of the development of weapons of mass destruction or military use. MITSUMI ELECTRIC CO., LTD. is not liable for any losses, damages, claims or demands caused by any provision or export to the person or entity who intends to develop, manufacture, use or store nuclear, biological or chemical weapons or missiles, or use any other military purposes.

- 8. The products are not designed to be used as part of any device or equipment that may affect the human body, human life, or assets (such as medical equipment, disaster prevention systems, security systems, combustion control systems, infrastructure control systems, vehicle equipment, traffic systems, in-vehicle equipment, aviation equipment, aerospace equipment, and nuclear-related equipment), excluding when specified for in-vehicle use or other uses by MITSUMI ELECTRIC CO., LTD. Do not apply the products to the above listed devices and equipment.

- MITSUMI ELECTRIC CO., LTD. is not liable for any losses, damages, claims or demands caused by unauthorized or unspecified use of the products.

- 9. In general, semiconductor products may fail or malfunction with some probability. The user of the products should therefore take responsibility to give thorough consideration to safety design including redundancy, fire spread prevention measures, and malfunction prevention to prevent accidents causing injury or death, fires and social damage, etc. that may ensue from the products' failure or malfunction.

- The entire system in which the products are used must be sufficiently evaluated and judged whether the products are allowed to apply for the system on customer's own responsibility.

- 10. The products are not designed to be radiation-proof. The necessary radiation measures should be taken in the product design by the customer depending on the intended use.

- 11. The products do not affect human health under normal use. However, they contain chemical substances and heavy metals and should therefore not be put in the mouth. The fracture surfaces of wafers and chips may be sharp. Be careful when handling these with the bare hands to prevent injuries, etc.

- 12. When disposing of the products, comply with the laws and ordinances of the country or region where they are used.

- 13. The information described herein contains copyright information and know-how of MITSUMI ELECTRIC CO., LTD. The information described herein does not convey any license under any intellectual property rights or any other rights belonging to MITSUMI ELECTRIC CO., LTD. or a third party. Reproduction or copying of the information from this document or any part of this document described herein for the purpose of disclosing it to a third-party is strictly prohibited without the express permission of MITSUMI ELECTRIC CO., LTD.

- 14. For more details on the information described herein or any other questions, please contact MITSUMI ELECTRIC CO., LTD.'s sales representative.

- 15. This Disclaimers have been delivered in a text using the Japanese language, which text, despite any translations into the English language and the Chinese language, shall be controlling.